Intime FPGA时序优化系统

-

系统介绍

随着FPGA规模越来越大,时序问题逐渐越来越严重,FPGA工程师会花费很大的精力在调试时序上,传统的方法就是修改代码或者针对时序路径进行优化,需要花费很大的精力,尤其当遇到需要针对功耗或者面积的优化时,更是非常棘手,而iNTIME时序优化系统则通过大数据分析和智能学习方式,自动化找到时序最佳收敛点,从而使整个FPGA设计时序更为优化,FPGA开发效率大大提高。

Intime 时序优化系统通过机器学习和大数据分析,通过运行不同的策略从而优化时序,使得时序最终能够收敛。自带有数据库,而且通过每次大数据分析进行不断升级,能够将最佳策略找出来,确保时序满足要求。

-

系统的特点

- 机器自学习和大数据分析,找到最佳策略;

- XILINX,ALTERA都能够完美支持;

- 自动化的管理多个FPGA工程的实现;

- 报告设计中影响时序的关键路径;

- 除了时序,还支持对资源和功耗的优化;

- 定制化高性能工作站,提高FPGA布局布线效率,快速达到用户满意的效果。

-

系统框图

FPGA时序优化系统由INTIME时序优化工具和APEX高性能工作站两部分组成

-

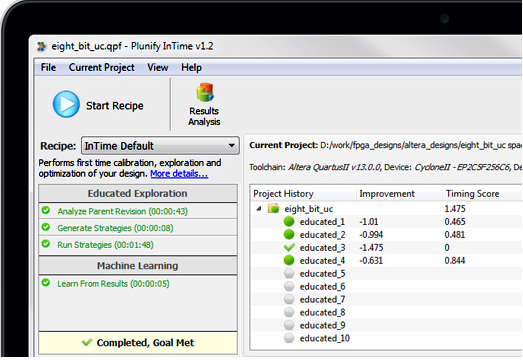

通过优化策略进行时序优化通过优化策略进行时序优化

通过优化策略进行时序优化,并能通过大数据分析,从而使得时序优化保持不断收敛,从而找到最佳时序。并且具有良好的时序优化界面。

支持Quartus,ISE和Vivado,只需配置好工具路径,iNTIME 会根据设计的器件,软件版本,自动生成策略,编译、布局布线、时序分析都是自动化完成。

-

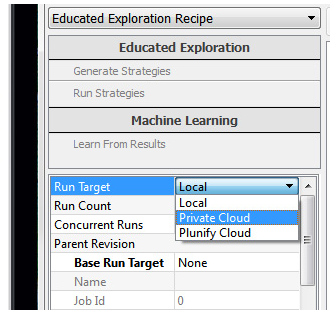

优化配置编译环境

能够优化配置工具软件运行环境,可以是工作站或者是采用Plunify的云平台,iNtime可支持并行编译,并发挥硬件的最佳性能,从而大幅度减少运行时间,整个流程无需人工参与。

-

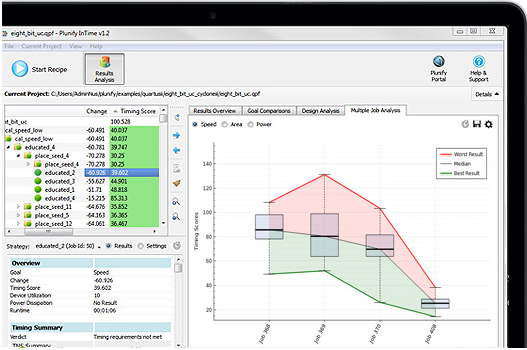

分析结果改善测量

分析所有的运行结果,并通过图表的方式产生统计数据,工程师不仅能够非常容易的了解编译结果,而且能够根据intime的设置参数,重现最佳结果。